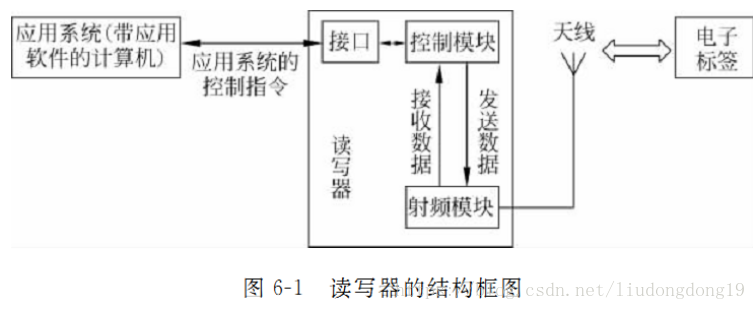

读写器的组成1.读写器的软件

读写器的所有行为均由硬件控制完成。软件向读写器发出读写命令,作为响应,读写器与电子标签之间经常搭建起特定的通信。软件负责平台的控制跟通信,包括控制天线发射的开关、控制读写器的工作方式、控制数据存储和控制命令交换。

2.读写器的硬件

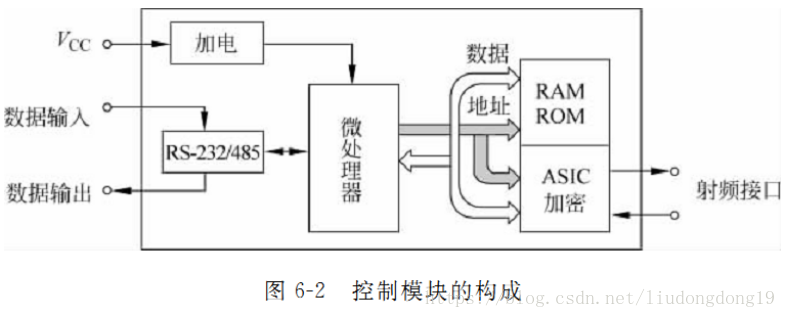

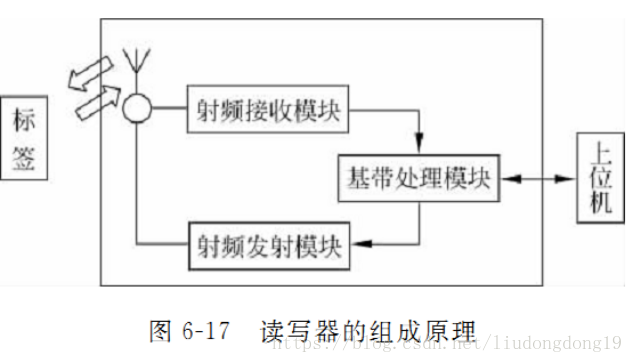

读写器的软件通常由天线、射频组件、控制模块和接口构成。控制组件是读写器的核心,一般由ASIC组件和微处理器组成。控制组件处理的讯号通过射频组件传送给读写器天线,由读写器天线发射出去。控制组件与应用工具之间的数据交换,主要借助读写器的接口来完成。

1)控制模块。

控制模块由ASIC组件和微处理器组成。微处理器是控制组件的核心配件。ASIC组件主要用来完成逻辑加密的过程,如对读写器与电子标签之问的数据流进行加密,以减少微处理器计算更加密集的负担。对ASIC的存取,是通过面向寄存器的微处理器总线实现的。

读写器的接口

读写器控制组件与应用工具之间的数据交换,主要借助读写器的接口来推动,接口可以运用RS-232、RS-485、RJ-45、USB2.0或WLAN接口。

读写器的设计要求

读写器在设计时必须考量许多原因,包括基本用途、应用环境、电器性能和电路设计等。读写器在设计时必须考量的主要原因如下。

1.读写器的基本用途跟应用环境

2.读写器的电气性能

3.读写器的电路设计

低频读写器:

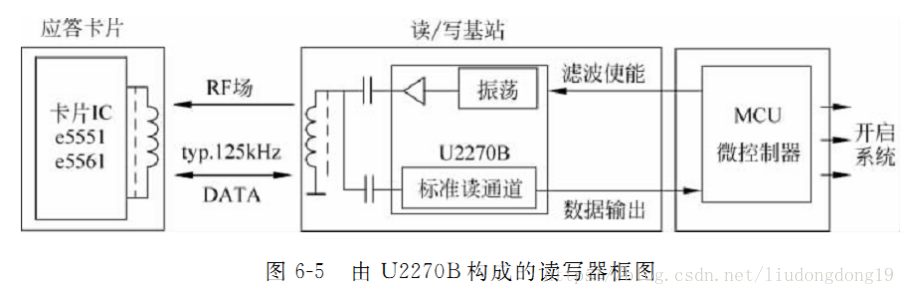

基于U2270B芯片的读写器

U2270B芯片的外部由振荡器、天线驱动器、电源供给电路、频率调节电路、低通滤波电路、高通滤波电路、输出控制电路等部份构成,其外部结构如图6-6所示。

高频读写器:

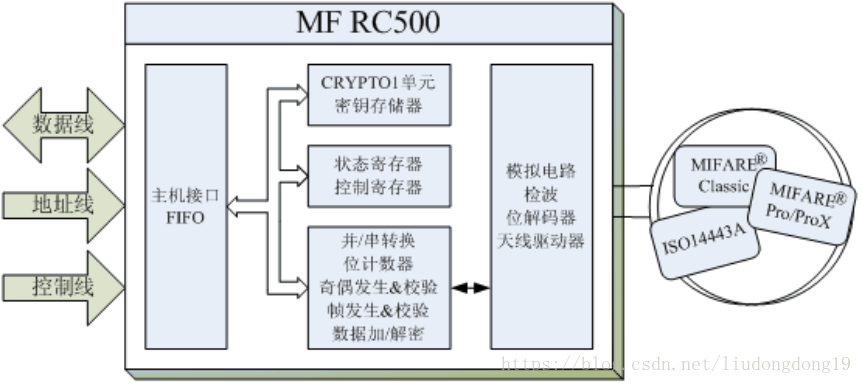

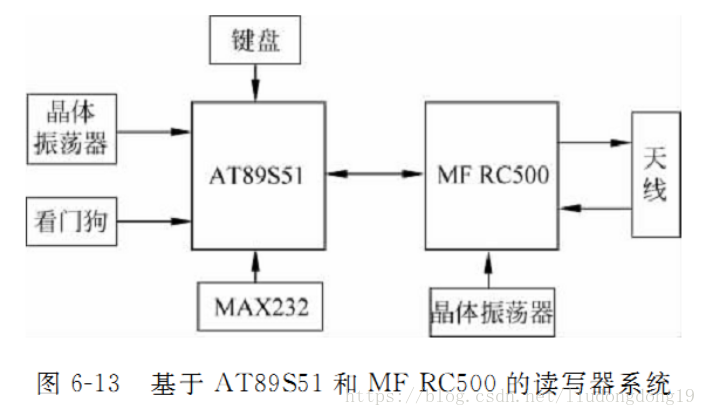

基于AT89S51和MF RC500的读写器系统

根据RFID原理跟MF RC500的特点,可设计基于AT 89S51和MF RC500的RFID读写器系统

微波读写器

系统软件设计与推动

1. 射频发射电路

射频发射电路完成载波以及调制讯号的发射。调制方法为ASK,调制深度采用100%,发射信号的输出衰减数字可控,使用FPGA进行配置。

2. 射频接收电路

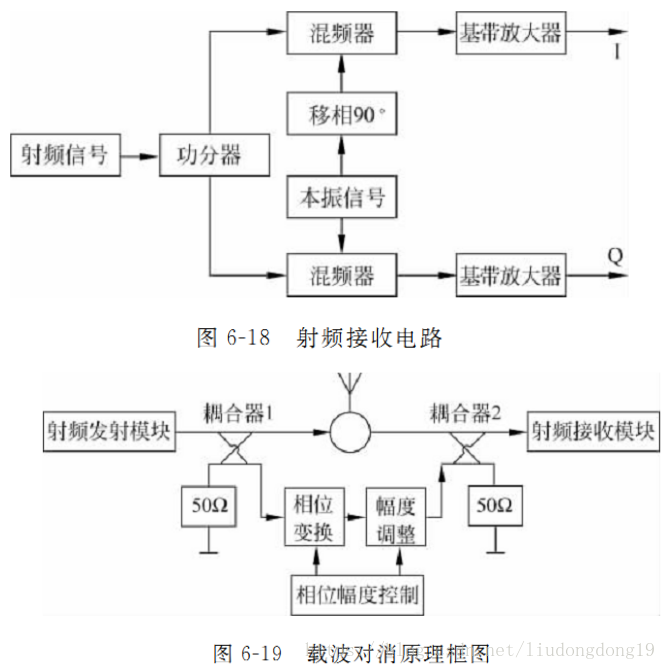

射频接收电路主要推动标签返回信号的解调。为减少后端DSP的处理难度,采用I、Q两路直接下变频的方法进行解调,如图6-18所示。

读写器工作过程中存在的一个主要难题是载波泄漏干扰。可以从下面两方面解决该难题。首先,采用ldB截止点较高的无源混频器进行滤波。其次,采用脉宽反馈回路抵消或减少泄漏的载波讯号。

基带处理电路

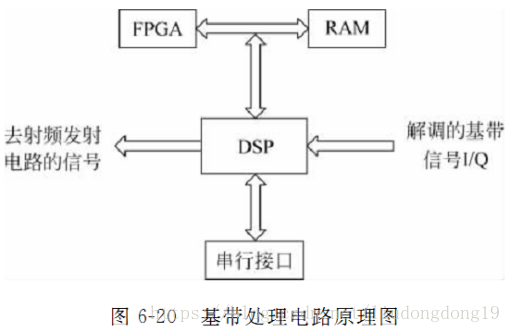

基带处理电路是整个电路的控制中心,提供整个读写器硬件电路的控制讯号,根据上位机的命令控制读写器的工作,包括编码、解码、CRC校验和防碰撞处理等。为了确保电路的处理速率跟能扩展性,在设计中引入了DSP芯片和FPGA芯片相结合的方法

读写器发送至标签的信号称为前向信号。前向信号的编码方法为曼彻斯特编码,标签到读写器的信号称为后向信号。后向信号的编码方法为FM0编码。FM0编码又称为差动双向码。

程序设计与实现:

FPGA程序

本设计中RFID读写器,FPGA主要提供平台时钟、RAM的读写控制逻辑或者调试过程中后向信号的逻辑仿真。内置PLL产生的稳定时钟供DSP使用;根据DSP读写逻辑及RAM的操作形成RAM的读写时序逻辑;根据应用环境的规定造成控制发射电路输出衰减的逻辑信号。另一方面,用FPGA生成调试过程中必须的标签返回的后向信号波形,以便于调试

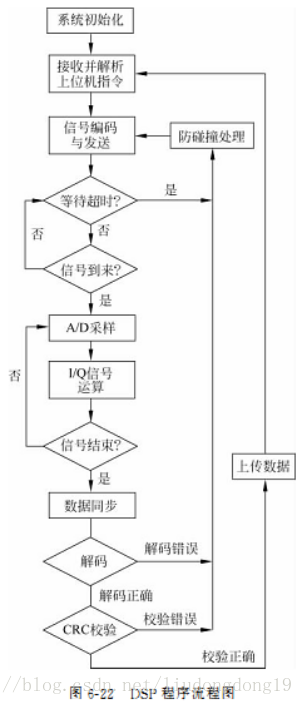

2. DSP程序

DSP主程序通过串行和上位机通信,接收并解析上位机指令,编码后发送给射频发射电路。从射频接收电路输出的I、Q两路信号,经A/D模块采样后,合成一路信号。主程序对此信号进行同步、FM0解码、CRC校验,得到最后数据,并将正确的数据上传至上位机中。如果FM0解码错误或CRC校验错误,则进行防碰撞处理。

防碰撞机制分析与推动

ISO 18000-6B协议中使用的是一类型二进制树形的防碰撞算法RFID读写器,通过标签内随机形成0、1及内置计数器实现标签的防碰撞。

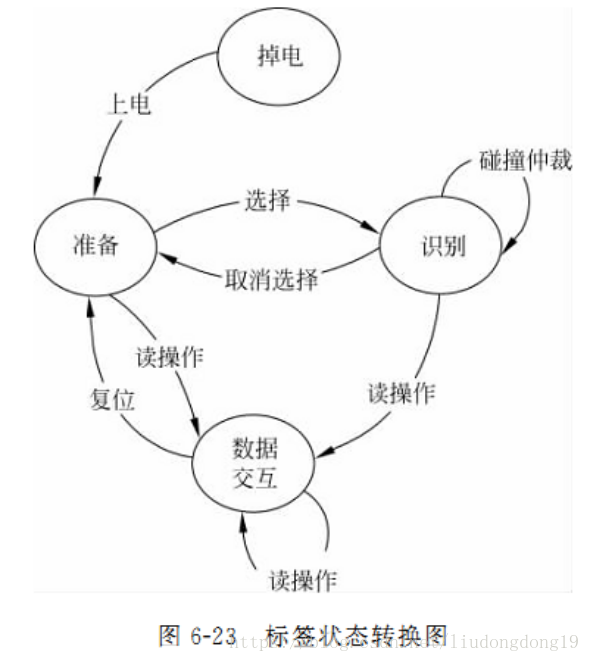

标签在工作过程中共有“掉电”、“准备”、“识别”和“数据交互”4个状态,其状况转换如图6-23 所示。

标签开启读写器的工作范围时,从离场“掉电”状态处于“准备”状态。读写器通过选择指令使进入“准备”状态的所有或个别标签开启“识别”状态。

当处于“识别”状态的标签多于一张时,就要借助碰撞仲裁实现标签的有效识别